e-ISSN: 2455-5703

# An Improved PDPWM for a Modular Multilevel Inverter used for Micro Grid

# <sup>1</sup>Rejoice Thomas Paul

<sup>1</sup>PG Student

<sup>1</sup>Department of Electrical and Electronics Engineering

<sup>1</sup>Adishankara Institute of Engineering and Technology

#### **Abstract**

This modulation method is based on selective virtual loop mapping, to achieve dynamic capacitor voltage balance without the help of an extra compensation signal. The concept of virtual sub module (VSM) is first established, and by changing the loop mapping relationships between the VSMs and the real submodules, the voltages of the upper/lower arm's capacitors can be well balanced. This method does not requiring sorting voltages from highest to lowest, and just identify the MIN and MAX capacitor voltage's index which makes it suitable for a modular multilevel converter with a large number of submodules in one arm. Compared to carrier phase-shifted PWM (CPSPWM), this method is more easily to be realized in field-programmable gate array and is conducive to the control of circulating current. Its feasibility and validity have been verified by simulations.

Keyword- Dynamic Voltage Balance (DVB), Modular Multilevel Converter (MMC), Phase disposition Pulse Width Modulation (PDPWM), Photovoltaic (PV), Selective Virtual Loop Mapping (SVLM)

## I. INTRODUCTION

In recent years, with the development of a large-scale photovoltaic (PV) power plant system, as well as smart grid and multilevel technologies, higher requirements in voltage level, modular structure, and flexibility and reliability of the next-generation large-scale PV grid-connected inverter have been put forward. The features include the following:

1) Power Peaking Capacity

PV systems should be able to store the electrical energy which is issued by itself as needed during light load conditions; meanwhile, this part of electrical energy would be released again for the load when the load is at the peak. As a result, the peak power of the grid and the reliability of power supply can be improved.

2) Fault Ride-Through Capacity

A large-scale PV system has been required to have the ability to withstand short periods of voltage abnormality, such as the voltage short-term drop caused by short-circuit fault. The PV system should maintain the connection of the inverter and the grid in addition to providing support to the grid.

3) Power Quality Control

More stable power supply performance could be achieved by introducing suitable inverter control strategy including voltage stability, phase regulation, active filter.

4) Higher Redundancy and Error Correction Capacity

The PV system should have the capacity to work efficiently when the failure occurs in some of the modules of the inverter system and should be "smart" enough to correct the situation.

The aforementioned requirements drive the research and development of the next-generation PV inverter, and the topologies of utility PV inverters are moving toward multilevel structure, which could provide better harmonic spectra and reduce the weight of the filtering components.

In many of the multilevel structures, a modular multilevel converter (MMC) has attracted many researchers recently. MMC-related application research has mostly concentrated on high-voltage direct current transmission, high-power motor drives, integrated energy storage and medium-voltage STATCOM. The MMC used in the PV grid-connected system is just mentioned in the reasons of this situation are as follows:

- 1) MMC related research is mostly in theoretical research stage.

- 2) The characteristic of the photovoltaic power generation is that PV panels are intermittent sources, and their output voltages continuously vary; the dc link's voltage has to be regulated to keep them working in maximum power point tracking (MPPT) status.

- 3) The dynamic voltage balance has to be considered in multilevel PWM, while the system stability would be damaged by adding improper signals to the reference voltage and the unique circulating current of the MMC will increase the system losses and is not conducive for improving the efficiency of the inverter output and the most important point is that the uncontrolled circulating current threatens the stability of the MMC. Among them, the first two points do not seem to be big problems,

because as a new modular converter for medium and high-voltage applications, the MMC has been tested and works well in a back-to-back structure and has much better four-quadrant performance. So, the third and fourth points are the keys to MMC used as a PV inverter. Many papers have discussed MMC modulation methods. The amplitude modulation has been widely used in the HVDC system; its core idea is to first calculate how many submodules should be put into action, and the capacitors' sorting voltage and the final working sequence should be determined by the direction of the arm current. The method is simple and practical, but there are frequent sorting issues with the capacitor voltage which would be a burden to the controller if the number of submodules is large. Phase-shifted pulse width modulation (PSPWM) is a more in-depth method and also studied in the field of MMC modulation. In order to balance the capacitor voltage, an extra signal generated by a PI regulator of each sub module has to be added to both the upper and lower arms' modulation signals. It means that a specialized balance controller has to be designed and with the increase of levels, the difficulty of control will increase and bring the risk of instability. At the same time, some new PWM methods have been proposed with different purposes, for example, the fundamental switching frequency modulation and the improved sub module unified PWM (SUPWM). This paper proposes a new selective virtual loop mapping (SVLM) method based on phase disposition PWM (PDPWM) which has voltage balance capability. The concept of virtual sub module (VSM) is established, and by changing the mapping routines between the VSM and the real sub module (RSM) with SVLM, the capacitor voltages of the upper and lower arms can be balanced even if the inverter loses its symmetry. The method has been designed to consider the following situations:

No extra signal should be added to the reference voltage to provide a good basis for the suppression of the circulating current.

- 1) The possibility of a large number of submodules in one arm.

- 2) Retain the equivalent switching frequency of the PDPWM.

- 3) It could be easily realized in field-programmable gate array (FPGA) for a large-scale converter which has a large number of submodules. The method is

- Verified through simulations and experiments. The modular multilevel converter (MMC) is an emerging and attractive topology for the high-voltage direct current (HVDC) transmission system. This paper presents a generalized mathematical model for MMC in HVDC applications under balanced and unbalanced grid conditions. The dynamics of the positive-, negative-, and zero-sequence components are derived from the model. Then, a dual current control scheme with positive and negative- equence current controllers is applied to MMC. The power controller to eliminate negative-sequence current components and the other one to eliminate double-line-frequency voltage ripple are compared. Moreover, a zero-sequence current controller is proposed in addition to the positive- and negative-sequence current controllers. Time-domain simulations on a 61-level MMCHVDC test system are performed in the PSCAD/EMTDC software environment. The results demonstrate that the MMC-HVDC system with or without converter transformer is able to operate under unbalanced conditions by the use of the proposed control scheme. [1] This paper makes an attempt to develop grid connected solar photovoltaic array power conversion using modular multilevel converter. The proposed system makes use of single stage power conversion with maximum power point tracking and modular multilevel converter (MMC) as interfacing unit into the grid. Here perturb & observe method of maximum power point algorithm is used to regulate the DC link voltage of the MMC and to synchronize the grid utility voltage with the current for attaining near unity power factor operation under varying environmental conditions. The simulation results presented in this paper verifies the operation of proposed MMC topology such that the AC output is free from the higher order harmonics and grid voltage and current are in phase. The simulation studies are carried out under power system computer aided design PSCAD/EMTDC 4.2 environment. [2]This paper presents the modular multilevel cascade converter (MMCC) family based on cascade connection of multiple reversible-chopper cells or multiple single-phase full bridge cells. This converter family are classified from circuit configuration as follows; single-star bridge-cells (SSBC), single delta bridge-cells (SDBC), double-star chopper-cells (DSCC), and double-star bridge-cells (DSBC). The term MMCC corresponds to a family name in a person while, for example, the term SSBC corresponds to a given name. Therefore, the term "MMCCSSBC" can identify the circuit configuration without any confusion. Among the four circuit configurations, SSBC and DSCC are the most practical than the others in terms of cost and performance, although a distinct difference exists in application between SSBC and DSCC. This paper describes applications of SSBC and DSCC to a battery energy storage system and a motor drive, respectively.[3] The modular multilevel converter (M2C) is a promising converter technology for various high-voltage high power applications. The reason to this is that low-distortion output quantities can be achieved with low average switching frequencies per switch and without output filters. With the M2C the output voltage has such a low harmonic content that high power motors can be operated without any derating. However, the apparent large number of devices, requires more complex converter control techniques than a two-level counterpart. Even though there have been several ways suggested to control the converter itself, it is still a challenge to investigate the interaction of these controllers with an external motor current controller. It is shown in the paper that the anticipated interaction will not result in any problems neither for the converter nor for the motor control itself.[4] This paper describes the operation of modular multilevel converter, an emerging and highly attractive topology for medium- and high-voltage applications. A new pulse width modulation (PWM) scheme for an arbitrary number of voltage levels is introduced and evaluated. On the basis of this PWM scheme, the semiconductor losses are calculated, and the loss distribution is illustrated.[5]The modular multilevel converter (MMC) is a newly introduced switch-mode converter topology with the potential for high-voltage direct current (HVDC) transmission applications. This paper focuses on the dynamic performance of an MMC-based, back-to-back HVDC system. A phasedisposition (PD) sinusoidal pulse width modulation (SPWM) strategy, including a voltage balancing method, for the operation of an MMC is presented in this paper. Based on the proposed PD-SPWM switching strategy, a mathematical model for the

MMC-HVDC system, under both balanced and unbalanced grid operation modes, is developed. Dynamic performance of the MMC-based back-to-back HVDC converter system, based on time-domain simulation studies in the PSCAD/EMTDC environment, is then evaluated. The reported time-domain simulation results show that based on the adopted PD-SPWM switching strategy, the MMC-HVDC station can respond satisfactorily to the system dynamics and control commands under balanced and unbalanced conditions while maintaining voltage balance of the dc capacitors.[6] This paper presents integrated level-shifted and phase-shifted multi carrier modulation schemes that ensures PWM and local capacitor voltage balancing of the Modular Multilevel Converter (M2LC) for medium voltage applications. The integration of either of the modulation schemes with the cell voltage balancing algorithm ensures the floating capacitor voltages are balanced throughout the operation of the M2LC voltage source converter. A comparison of the two schemes is presented based on the harmonic content of the synthesized output waveforms and peak to-peak ripple of the local capacitor voltages. The converter semiconductor losses are also evaluated and compared for these modulation schemes in a typical medium voltage grid application. It is shown that both schemes are competitive in terms of the synthesized output waveform quality. However the phase shifted scheme offers less capacitor voltage ripple while the level shifted scheme offers low converter loss. The concepts are confirmed with both PLECS simulation package and a 10kVA 9-level experimental prototype.[7]

The above Phase-shifted pulse width modulation (PSPWM) is a more in-depth method and also studied in the field of MMC modulation. In order to balance the capacitor voltage, an extra signal generated by a PI regulator of each submodule has to be added to both the upper and lower arms' modulation signals. It means that a specialized balance controller has to be designed and with the increase of levels, the difficulty of control will increase and bring the risk of instability. At the same time, some new PWM methods have been proposed with different purposes, for example, the fundamental switching frequency modulation and the improved submodule unified PWM (SUPWM).

## II. PROPOSED METHOD

#### A. Phase Disposition PWM

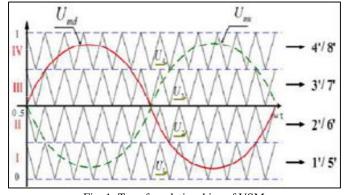

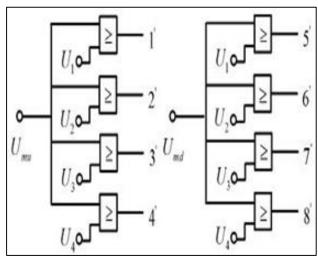

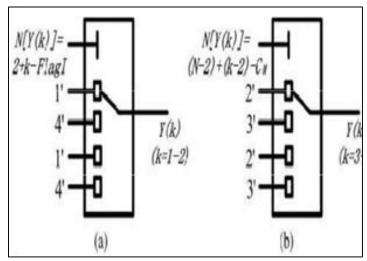

To overcome the previous disadvantages we proposed a new selective virtual loop mapping (SVLM) method based on phase disposition PWM (PDPWM) which has voltage balance capability. The concept of virtual submodule(VSM) is established, and by changing the mapping routines between the VSM and the real submodule(RSM) with SVLM, the capacitor voltages of the upper and lower arms can be balanced even if the inverter loses its symmetry. The method has been designed to consider the following situations: 1) no extra signal should be added to the reference voltage to provide a good basis for the suppression of the circulating current; 2) the possibility of a large number of submodules in one arm; 3) retain the equivalent switching frequency of the PDPWM; 4) it could be easily realized in field-programmable gate array (FPGA) for a large-scale converter which has a large number of submodules. As an important modulation method, carrier disposition (CD) PWM has been widely used in multilevel modulation, and it can be divided into three types: phase disposition (PD), phase opposition disposition (POD), and alternative phase opposition disposition (APOD). For simplicity, this paper will focus on the PDPWM to discuss MMC modulation. PDPWM has been studied for MMC modulation in order to balance capacitor voltages, rotating carrier waves were used, but it seems that they can only work under symmetric condition. For convenience, it is assumed that the number of RSMs of the upper and lower arms is 4 (= 4). And the RSMs are numbered from to 8 (from top to bottom). The difference of the capacitor voltage can be greatly reduced, and the system output voltage and current waveforms are improved. Since no additional signals are added to the reference voltage, the overall characteristics of the MMC do not need to be changed, such as the internal circulating current, which can be observed this characteristic provides a good basis to eliminate the circulating current further. To improve the PDPWM, the concept of VSM can be first established, which means that the VSMs are not the RSMs, and the PWM output gained by the comparison of the modulation signals and the carriers will be transferred to the VSM at first, and VSMs are numbered by 1' to 2N'. The transfer relationships are illustrated as Figs. 3 and 4. According to Figs. 1 and 2, 2N + 1 level modulation truth table can be shown as in Table I. 1' to 4' are for the upper arm's VSMs, while 5' to 8' represent the lower arm's VSMs. Here, "1" means that the corresponding VSM is ON while "0" means that it is OFF.

Fig. 1: Transfer relationships of VSM

Fig. 2: VSM's input

| Region | ľ      | 21     | 3'     | 4'     | 5"     | 6'     | 7*     | 8'     | Range of<br>normalize<br>d voltage |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------------------------------|

| I      | P<br>I | 0      | 0      | 0      | P<br>5 | 0      | 0      | 0      | 0-0.25                             |

| И      | I      | P<br>2 | 0      | 0      | I      | P<br>6 | 0      | 0      | 0.25-<br>0.5                       |

| Ш      | I      | I      | P<br>3 | 0      | I      | 1      | P<br>7 | 0      | 0.5-<br>0.75                       |

| IV     | I      | I      | 1      | P<br>4 | I      | 1      | 1      | P<br>8 | 0.75-1                             |

Table 1: Witch Combinations of VSM (2n + 1 Level)P1-P8 is the corresponding PWM signals of each VSM's input

| Region | I'     | 2'     | 3′     | 4'     | 5'     | 6'     | 7*     | 8′     | Range of<br>normalize<br>d voltage |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------------------------------|

| I      | P<br>I | 0      | 0      | 0      | P<br>5 |        |        |        | 0-0.25                             |

| И      | I      | P<br>2 | 0      | 0      | 0      | P<br>6 |        |        | 0.25-<br>0.5                       |

| Ш      | I      | I      | P<br>3 | 0      | 0      | 0      | P<br>7 |        | 0.5-<br>0.75                       |

| IV     | I      | I      | 1      | P<br>4 | 0      | 0      | 0      | P<br>8 | 0.75-                              |

Table 2: Switch Combinations of VSM (n+ level)

P5-P8 is the corresponding negative PWM signal of P1-P4 respectively

P1–P4 are the comparison results of the carriers and the modulation signals. The range of normalized voltage corresponds to Regions I–IV. In each region, each VSM has its own PWM signal. For example, when the modulation signal Umu is in Region II, P2 and P6 will be transferred to VSMs 2' and 6', while at the same time, "1" will be output to VSMs 1' and 5', and "0" will be output to VSMs 3', 4', 7, ' and 8'. Other regions can also be analyzed like this. Table II shows the N + 1 level modulation, compared with Table I; the driving signals of the lower arm's VSMs are complementary to the upper arm. Because the 2N + 1 level modulation has higher dc-link voltage ripple, this paper chooses the N + 1 level modulation as the PV grid-connected inverter's

modulation method. The driving signals of VSMs would be transferred to the RSM by the following mapping rules described in the next section.

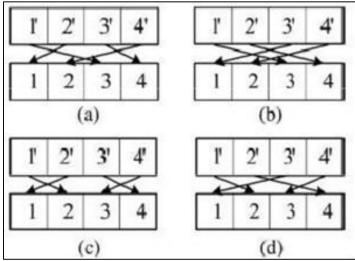

Fig. 3: VLM's mapping relationship. (a) Upper arm's mapping. (b) Lower arm's mapping

## III. CAPACITOR VOLTAGE VIRTUAL LOOP MAPPING BALANCE CONTROL

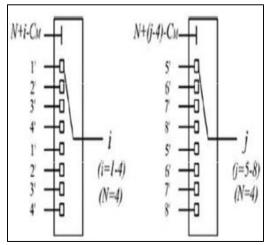

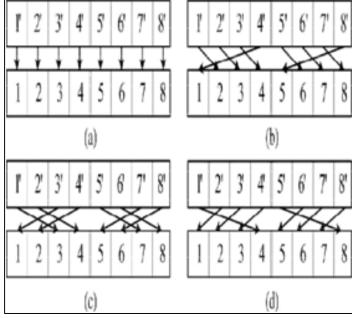

To solve the submodule capacitor voltage balance control problems, there are two mechanisms: the virtual loop mapping (VLM) method and the enhanced SVLM based on the comparison of capacitor voltage MIN and MAX values. The VLM's principle is using a count-up counter "CM" to control the mapping relationships between the VSMs and the RSMs. The CM 's working frequency can be set equal to the carrier frequency or less, and its counting range is 0 - (N - 1). Different counter number means different mappings. The VLM can be realized easily by using multiplexer with single-pass transistor in FPGA like Fig. 4 (N = 4); the double input buffer (DIB) structure is also used here. i and j in Fig. 3 are the index numbers of the RSM, respectively, which work with the counter to realize the mapping between the VSMs and the RSMs. For example, if CM = 0, + i - CM = 4 + i - 0 4 + i, VSMs 1'-2'-3'-4' would be mapped to RSMs 1-2-3-4 as shown in Fig.4(a); likely, if CM = 1, N + i - CM = 4 + i - = 3 + i, VSMs 4'-1'-2'-3' would be mapped to RSMs 1-2-3-4 [see Fig. 4(b)], and so on. The VLM's final results of both arms are illustrated in Fig. 5. This method can achieve capacitor voltage balance in the case of system symmetry.

## IV. CAPACITOR VOLTAGE SVLM BALANCE CONTROL

A practical modulation method should not only be effective in a symmetrical system, but also have the ability to regulate dynamically and provide some error finding to correction capabilities to ensure that the system works well under conditions such as error accumulation and device parameter deviation. For the basic cells in the upper bridge, the capacitors are bypassed at onstate and charged at off-state when iPa > 0. For the basic cells in the lower bridge, the capacitors are discharged at on-state and bypassed at off-state when iNa > 0. For the middle cell, the capacitor is discharged at on-state and charged at off-state when ioa > 0, where ioa is the phase current and is the sum of iPa and iNa. For example, commonly used phase-shift PWM, by changing the modulation signals of the upper and lower arms to get the dynamic balance adjustment capacity of the capacitor voltage, will bring more harmonics to the arm current, change the circulating current' characteristics, and may cause instability. Therefore, changing the modulation signals to achieve the dynamic adjustment capability would be valid only to a certain extent. The new method is mainly through the SVLM to achieve the effect of dynamic regulation ability; here, "selective" means just taking out the capacitor voltage of MIN and MAX values and their corresponding index selectively.

Fig. 4: Upper arm's VLM procedures

Fig. 5: VLM final results. (a) CM = 0. (b) CM = 1. (c)  $\overline{CM = 2$ . (d)  $\overline{CM = 2}$

Before introducing the SVLM rules, note that there are four interesting SMs in Table II, which are 1', 4', 5', and 8'. VSMs 1' and 8' output PWM in regions and IV, respectively, and output "1" in other regions. Likewise, VSMs 4' and 5' output PWM in regions IV and I, and output "0" in other regions. Table V shows that if some capacitor voltage of the leg is less than the others (means needing more charge and less discharge), it would be right to map the SMs 1' and 8' to this submodule when the corresponding current sm is positive and mapping the SMs 4' and 5' to it when sm is negative. To achieve the SVLM, it needs to sort the capacitor voltage as described, but frequent sorting is very time consuming, and requires more hardware resources, which would be a large burden especially for high-voltage applications needing more submodules. Other disadvantages of sorting are a reduction in system equivalent frequency and an increase in switching losses. Therefore, the actual method of selective mapping in this paper is just picking the MIN and MAX capacitor voltages and their corresponding index directly and make sure that it can be easily implemented in FPGA. The rules of the SVLM are as follows (just taking the upper arm as an example).

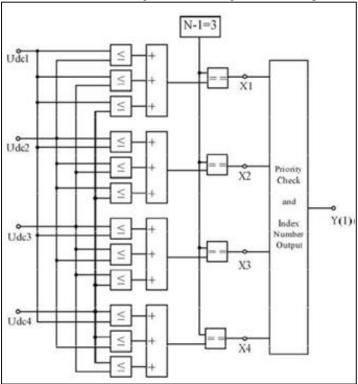

#### 1) First, all of the individual capacitor

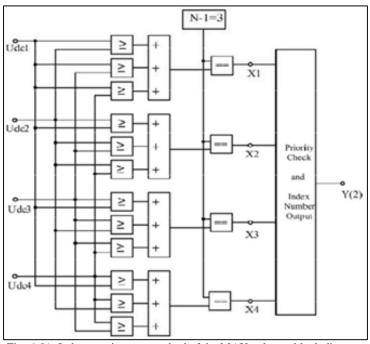

Voltages are compared, and the corresponding RSM indexes of the maximum voltage and minimum voltage are obtained. The MIN index block diagram is shown in Fig. 6(a) (N = 4). Y is an array, and Y (1) is the first element. Udc1 – U dc4 are the SM's capacitor voltage of the upper arm separately and they are compared to each other at the same time which means that the time is limited. Y (1) would be equal to the capacitor index having the minimum voltage: for example, if the voltage of Udc3 is the minimum, Y (1) would be equal to 3. Priority check is just for the case of more than one input of X1–X4 equal to 1, so that X1 could be set up to the highest priority in the MIN check, while X4 has the lowest priority. For the MAX check, " $\leq$ " would be replaced by " $\geq$ ," while Y (2) provides the corresponding index of the maximum capacitor voltage [see Fig. 6(b)], and X4 should have the highest priority while X1 should have the lowest priority.

- 1) The corresponding truth table of the priority check and index number output function for Y (1) is shown in Table 3 Y

- 2) Can be acquired by the same method (see Table 4).

| XI | <i>X</i> 2 | <i>X3</i> | <i>X4</i> | <i>Y</i> (1) |

|----|------------|-----------|-----------|--------------|

| 1  | х          | х         | х         | 1            |

| 0  | 1          | х         | х         | 2            |

| 0  | 0          | 1         | х         | 3            |

| 0  | 0          | 0         | 1         | 4            |

Table 3: Priority Check and Index Number Output Truth Table of Y(1)

| X means any state. |            |           |           |              |  |  |  |

|--------------------|------------|-----------|-----------|--------------|--|--|--|

| XI                 | <i>X</i> 2 | <i>X3</i> | <i>X4</i> | <i>Y</i> (2) |  |  |  |

| х                  | х          | х         | 1         | 4            |  |  |  |

| х                  | х          | 1         | 0         | 3            |  |  |  |

| х                  | 1          | 0         | 0         | 2            |  |  |  |

| 1                  | 0          | 0         | 0         | 1            |  |  |  |

Table 4: Priority Check and Index Number Output Truth Table of Y (2)

X means any state

3) The other SMs' indexes except the minimum and maximum capacitor voltages would also be assigned to the Y array by sequence after Y (2). The main difference between them is that the proposed new MMC employs a middle cell in each phase,

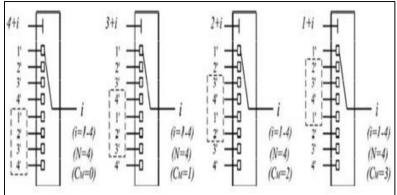

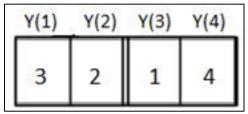

which can reduce the number of basic cells while producing the same number of voltage levels. Of course, it also has some drawbacks due to the employment of middle cell, such as that the voltage balancing becomes more complex and the redundancy of middle cell is hard to realize. For example, if SM 3 has the lowest voltage and SM 2 has the highest voltage, the Y array would be assigned like this, as shown in Fig. 7. 4) Change the mapping route as shown in Fig. 8,N[Y (i)] is the multiport switch selector array, whose index is Y (i) (= -4). FlagI is the symbol of the arm's current direction. If the upper arm's current is positive (Ijp > 0), FlagI = 0; [Y (1)] would be equal to 3, which means that VSM 1'would be mapped to RSM 3. At the same time, N[Y (2)] would be equal to 4, andVSM4' would be mapped to RSM 2. In contrast, if Ijp < 0, FlagI = 1, N[Y (1)] is assigned to 2, and VSM 4' is mapped to RSM 3, while VSM 1' is mapped to RSM 2. The rest of the mappings follow the aforementioned VLM, as can be seen in Fig. 8. Just take Fig. 7 as an example.

Fig. 6 (a): Index acquirement method of the MIN voltages block diagram

Fig. 6 (b): Index acquirement method of the MAX voltages block diagram

If Ijp > 0 N [Y (1)] = N [3] = 3 N [Y (2)] = N [2] = 4

Fig. 7: Assignment of the Y Array

Fig. 8: Mapping route control of each RSM

Fig. 9: SVLM. (a) CM = 0. (b) CM = 1 (c) CM = 0. (d) CM = 1

If Ijp < 0

N[Y(1)] = N[3] = 2

N[Y(2)] = N[2] = 3

At the same time, the rest of the RSMs would still follow the previously described VLM rule. But the maximum counter range of CM would be set equal to N-2. If CM=0

N[Y(3)] = N[1] = 3

N[Y(4)] = N[4] = 4.

If CM = 1

N[Y(3)] = N[1] = 2

N[Y(4)] = N[4] = 3.

4) The final mapping route would be as follows

Ijp>0(j = a, b, c), SVLM is given in Fig. 9

Ijp>0(j = a, b, c), SVLM is given in Fig. 9

- (a) and (b). Ijp<0(j = a, b, c), SVLM is given in Fig. 9 (c) and (d).

- 5) In order to minimize the delay of the PWM signal, a synchronous sampling control should be adopted to the SVLM .Umu is the reference voltage, and Y array is sampled at the intersection point of two triangular carriers.

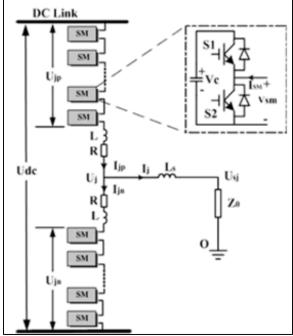

#### V. OPERATING PRINCIPLE OF PHASE DISPOSITION PWM METHOD

#### A. Modulation Principles

Fig. 10 shows the single-phase equivalent circuit of the MMC, which has two arms including the upper arm and the lower arm, with each arm having N submodules (SM), one buffer inductor L, and equivalent resistor R. The dc link of the MMC is floated or connected to high-voltage sources depending on the working purpose of the converter. The output of the converter is the connection point of the upper and lower arms. Ls is the ac-link inductor, and Z0 is the equivalent impedance of the ac side. The working states of SM are shown in TableV. Each SM has two states ("ON" and "OFF"), and the corresponding output voltage (Usm) of the SM is Vc or 0.

Fig. 10: Single phase equivalent circuit of multilevel converter

The capacitor will charge or discharge during the period of the "ON" state of the SM depending on the direction of sm. For example, if Ism > 0, the capacitor would be charged, and if Ism < 0, the capacitor would be discharged.

| МО | S | S | Us | Is | STA | CAPACI          |

|----|---|---|----|----|-----|-----------------|

| DE | 1 | 2 | m  | m  | TE  | TOR             |

| 1  | 1 | 0 | Vc | >0 | O n | Charging        |

| 2  | 1 | 0 | Vc | <0 | O n | Dischargi<br>ng |

| 3  | 0 | 1 | 0  | >0 | Of  | Unchange<br>d   |

| 4  | 0 | 1 | 0  | <0 | Of  | Unchange<br>D   |

Table 5: Half-Bridge Subm Odule Working States

The capacitor voltage will be kept while the SM is "OFF." Seen from Fig. 1, the j phase output voltage Uj can be expressed as (j = a b, c)

$$Uj=1/2 [Ujn+L(dIjn/dt)+IjnR]-1/2[Ujp+L(dIjp/dt)+I$$

(1)

where Ujp represents the sum of the upper arm's capacitor voltage while Ujn represents the sum of the lo wer arm's capacitor voltage. Ijp and Ijn are the upper arm's current and the lower arm's current, respectively. L and R are the buffer inductor and resistor of the arm.

```

2Uj = (Ujn-Ujp)+L d(Ijn-Ijp)/dt + R(Ijn-Ijp)

(2)

Ij=Iip-Ijn

(3)

Icirc j = Ijp + Ijn/2

(4)

2Uj = (Ujn - Ujp) - LdIjdt - RIj

(5)

Udc = (Uin + LdIindt + RIin + LdIindt + RIip) = (Uin + Uip) + Ld(Iin + Iip)dt + (Iin + Iip)

= (Ujn + Ujp) + 2L(dIcirc j/dt) + 2RIcircj

L(dIcircidt)+RIcirci=1/2(Udc-Ujp-Ujn)

(7)

Defining two variable as e and Ucirci as the following equations:

e = 1/2(Ujn - Ujp)

(8)

Ucirc j = L(dIcircj/dt) + RIcircj = 1/2(Udc - U jp - Ujn)

(9)

From (8) and (9), the reference signals of upper and lower arms can be expressed by

Ujp=1/2(Udc-e-Ucirj) & Ujn=1/2(Udc +e-Ucirj)

(10)

```

Where Ucircj can be used to suppress the circulating current.

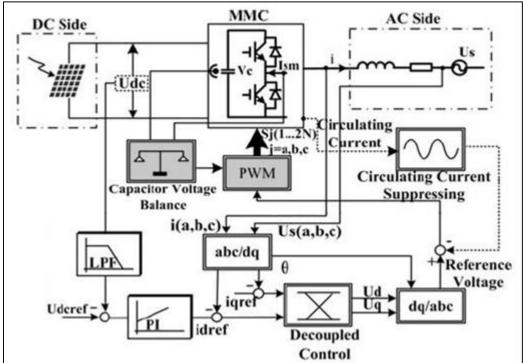

#### B. Basic Structure and Control

There are two structures which can be used in medium- and high-voltage PV grid-connected inverters with MMC: single stage and two-stage structure es. The series-connected PV modules of a single-stage structure access the dc link directly, while in a two-stage structure the procedure is different: PV panels could be connected to the dc link by cascaded dc/dc circuits [24], The differences are that voltage ripples of the single stage structure are bigger than those of the two-stage structure, and the two-stage structure has more complex control [26]. Fig. 11 shows the control block diagram of a modular multile vel PV inverter where Udcref is the reference of the dc-link voltage and Udc is the real d c-link voltage; they are compared with each other to produce the active reference e current idref after the PI controller, iqref is the reactive reference current. Us (a, b, c) is the ac-side grid voltage and I (a, b, c) is the output current of the MMC. Sj  $(1, \ldots, 2N, j = a, b, c)$  are the PWM signals of the M MC. It can be seen that the reference v oltage can be acquired by decoupled co ntrol, and the circulating current suppression compensation signal should be added to it. Meanwhile, it is no longe r possible to balance the system capa citor voltage dynamically by generating the appropriate balance compensation signal , but solely by the adjustment of the PWM method. This approach has the advantage e of not only avoiding excessive compensation signal mutual interference (which in creases system stability), but also provides a good basis for circulating current suppression n and promotes high dc voltage utilization ratio.

Fig. 11: Modular multilevel PV inverter overall control block diagram

| PARAMETER S      | VALUES |

|------------------|--------|

| No.of PV panel s | 4      |

| No of sub-module s in each arm | 4            |

|--------------------------------|--------------|

| Sub-module Capacitor           | 2200 uF      |

| Arm Inductor L                 | 2 mH         |

| Arm Equivalent  Resistance     | 0.1 Ώ        |

| AC Link Inductor Ls            | 5 mH         |

| Carrier frequency              | 2400 Hz.     |

| AC system voltage Us  (rms)    | 115 V        |

| ,                              |              |

| Power frequenc y               | 60 Hz        |

| Transformer                    | 600 V/ 240 V |

Table 6: Simulation and Experiment Param Eters

## VI. EXPECTED RESULTS

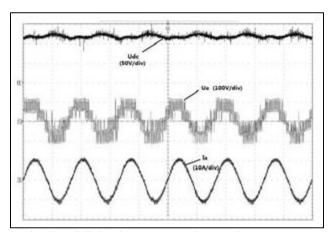

Fig. 12: DC-link voltage, output voltage, and output current

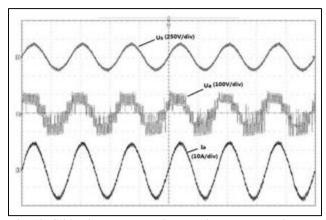

Fig. 13: Grid voltage, output voltage, and output current inverter

# VII. CHALLENGES IN PRO POSED CONVERTER

The capacitor voltages of the upper and lower arms can be balanced even if the inverter loses its symmetry. The method has been designed to consider the following situations: 1) no extra signal should be added to the reference voltage e to provide a good basis for the suppression of the circulating current; 2) the possibility of a large number of submodules in one arm; 3) retain the equivalents

witching frequency of the PDPWM; 4) it could be easily realized in field-programmable gate array (FPGA) for a large-scale converter which has a large number of submodules.

## VIII. CONCLUSION

This paper first discussed the possibilities of the M MC being used as an interface between the grid and PV panels, and proposed an imp roved SVLM method based on the PD PW M. This method can produce 2 + and N + 1 level outputs in the MMC, and achieve submodule capacitor voltage dynamic balance compensation control while not changing the reference signal. The whole mapping rules are presented and it is easy to be implemented in FPGA and the effect iveness of the method was proved well.

## REFERENCES

- [1] M. Guan and Z. Xu, "Modeling and control of a modular multilevel converter-based HVDC system under unbalanced grid conditions," IEEE Trans. Power Electron., vol. 27, no. 12, pp. 4858–4867, Dec. 2012.

- [2] Jasekar and R. Gupta, "Solar photovoltaic power conversion using modular multilevel converter," in Proc. Student Conf. Eng. Sy st., 2012, pp. 1-6.

- [3] H.Akagi, "Classific ation, terminology, and application of the modular multilevel cascade converter (MMCC)," IEEE Trans. Power Electron.,vol. 2 6, no. 11, pp. 3119–130,Nov.2011.

- [4] G. P. Adam, S. Fi nney, and B. Williams, "Analysis of modular multilevel converter capacitor voltage balancing based on phase voltage redundant states," IET Power Electron. J., vol. 5, no. 6, pp. 726–738, 2012.

- [5] S. Rohner, S. Bernet, M. Hiller, and R. Sommer, "Modulation, loses and semiconductor requirements of modular multilevel converters," IEEE Trans. Ind Electron., vol. 57, no. 8, pp. 2633–2642, Aug. 2010.

- [6] E. K. Amankwah, J. C. Clare, P. W. Wheeler, and A. J. Watson, "Multi carrier PWM of the modular multilevel VSC for medium voltage applications," in Proc. IEEE Appl. Power Electron. Conf. Expo., 2012, pp. 2398–2406.

- [7] S. Sedghi, A. Dastfan, and A. Ahmadyfard, "A new multilevel carrier based pulse width modulation method for modular multilevel inverter," in Proc. IEEE Conf. Power Electron. ECCE Asia, Jeju, Korea, 2011, pp. 1432–1439.

- [8] E. K. Amankwah, J. Clare, P. W. Wheeler, and A. J. Watson, "Multi carrier PWM of the modular multilevel VSC for medium voltage applications," in Proc. IEEE Appl. Power Electron. Conf. Expo., 2012, pp. 2398–2406.

- [9] I. Abdalla, J. Corda, and L. Zhang, "Multilevel DC-link inverter and control algorithm to overcome the PV partial shading," IEEE Trans. Power Electron., vol. 28, no. 1, pp. 14–18, Jan. 2013.

- [10] M. Hagiwara, R. Maeda, and H. Akagi "Control and analysis of the modular multilevel cascade converter based on double-star chopper-cells (MMCC-DSCC)," IEEE Trans. Power Electron., vol. 26, no. 6, pp. 1649–1658, Jun. 2011.

- [11] M. Hagiwara and H. Akagi, "Control and experiment of pulse width modulated modular multilevel converters," IEEE Trans.Power Electron., vol. 24, no. 7, pp. 1737–1746, Jul. 2009.

- [12] H. A latrash, R. A. Amarin, and C. Lam, "Enabling large-scale PV integration into the grid," in Proc. IEEE Green Technol. Conf., 2012, pp. 1-6.

- [13] Z. Li, P. Wang, H. Zhu, Z. Chu, and Y.Li, "An improved pulse width modulation method for chopper-cell-based modular multilevel converters," IEEE Trans. Power Electron., vol. 27, no. 8, pp. 3472–3481, Aug.2012.

- [14] H. P.Mohammadi and M. T. H. Bina, "A transformer less medium-voltage STATCOM topology based on extended Modular multilevel converters," IEEE Trans. Power Electron., vol. 26, no. 5, pp. 1534–1545, May 2011.

- [15] B. Alajmi, K. H. Ahmed, G. P. Adam, J. Finney, and B. W.Williams, "Modular multilevel inverter with maximum power point tracking for grid connected photovoltaic application," in Proc. IEEE Int. Symp. Ind. Electron. 2011, pp. 2057–2062.

- [16] M. Hagiwara and H. Akagi, "Control and experiment of pulse width modulated modular multilevel converters," IEEE Trans. Power Electron.

- [17] Q. Tu, Z. Xu, and L. Xu, "Reduced switching-frequency modulation and circulating current suppression for modular multilevel converters," IEEE Trans. Power Del., vol. 26, no. 3, pp. 2009–2017, Jul. 2011.

- [18] Y. Xue, K. C. Divya, G. Griepentrog, M. Liviu, S. Suresh, and M. Manjrekar, "Towards next generation photovoltaic inverters," in Proc. IEEE Energy Convers. Congr. Expo. 2011, pp. 2467–2474.

- [19] R. K. Varma, V. Khadkikar, and R.Seethapathy, "Nighttime application of PV solar farm as STATCOM to regulate grid voltage," IEEE Trans. Energy Convers., vol. 24, no. 4, pp. 983–985, Dec. 2009.

- [20] L. Liu, H. Li, Z. Wu, and Y. Zhou, "A cascaded photovoltaic system integrating segmented energy storages with self-regulating power allocation control and wide range reactive power compensation," IEEE Trans. Power Electron., vol. 26,no. 12, pp. 3545–3559, Dec. 2011.